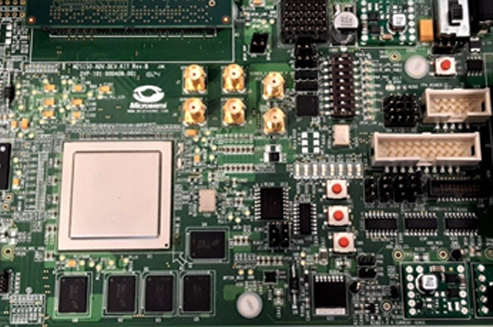

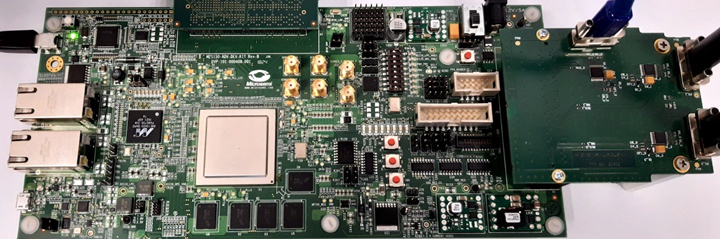

Projekt Flash Memory Module (FMM) polega na rozwoju układu FPGA kontrolującego pamięć masową typu Flash oraz zabezpieczającego gromadzone dane przed ich utratą wskutek działania promieniowania kosmicznego. Prace dotyczą rozwoju wykorzystania technologii pamięci w warunkach środowiska docelowego. Projekt FMM jest realizowany we współpracy z Europejską Agencją Kosmiczną, a firma SYDERAL Polska jest głównym jego wykonawcą.

Jedną z kluczowych wartości projektu jest implementacja w układzie FPGA rozwiązania ochrony zapisywanych i odczytywanych z pamięci danych, pozwalającego na nieprzerwany zapis pomimo nagłego zablokowania pamięci Flash oraz odzyskanie odczytywanych danych nawet jeśli jedna z pamięci uległa uszkodzeniu lub czasowemu zablokowaniu.

„Rozwój technologii modułów pamięci masowej Flash w zastosowaniach kosmicznych to jedna z kluczowych kompetencji naszej firmy, którą konsekwentnie rozwijamy. Kontynuacja prac w ramach projektu Flash Memory Module i znalezienie użytkownika końcowego dla stworzonych rozwiązań to niewątpliwie efekt sukcesu pierwszej fazy projektu. Jednocześnie cieszymy się, że ESA wspiera rozwój tej technologii. Dzięki tego typu projektom polskie firmy sektora kosmicznego umacniają swoją pozycję na europejskim i światowym rynku” – mówi Tadeusz Kocman, kierownik ds. rozwoju biznesu w SYDERAL Polska.

Użytkownikiem końcowym technologii będzie firma RUAG Space, która pomoże w ustaleniu wymagań oraz uczestniczyć będzie w przeglądach technicznych projektu. Łączny budżet projektu wynosi blisko 0,4 mln €, a zakończenie prac planowane jest na drugi kwartał 2023 roku.

„RUAG Space jest wiodącym dostawcą oraz integratorem podsystemów dla komercyjnych i instytucjonalnych klientów z branży kosmicznej w Europie i USA. Cieszymy się ze współpracy z SYDERAL Polska w rozwijaniu nowej generacji pamięci masowych, np. dla ładunków użytecznych, oraz liczymy na dalszą współpracę związaną z tym produktem w przyszłości” – tłumaczy Viktor Fägerlind, Senior Manager Product Portfolio, Satellite Avionics w RUAG Space.

W zakończonej w grudniu 2021 r. pierwszej fazie projektu prędkość wszystkich interfejsów została zwiększona dwukrotnie (do 200 MHz), a komunikacja z modułem dostosowana do istniejących wymagań technicznych dotyczących pamięci masowych dla misji ARIEL. W ramach drugiej fazy projektu prędkość interfejsów zostanie zwiększona do 1.25Gbps, kontroler pamięci Flash zaimplementowany zostanie na układzie lotnym FPGA, a obsługiwana pamięć Flash zwiększona będzie czterokrotnie – do 2 Tb.

Źródło: informacja prasowa